- 您现在的位置:买卖IC网 > Sheet目录3818 > PIC18F4620-I/ML (Microchip Technology)IC MCU FLASH 32KX16 44QFN

PIC17C4X

DS30412C-page 46

1996 Microchip Technology Inc.

7.2

Table Writes to External Memory

Table writes to external memory are always two-cycle

instructions. The second cycle writes the data to the

external memory location. The sequence of events for

an external memory write are the same for an internal

write.

Note:

If an interrupt is pending or occurs during

the TABLWT, the two cycle table write

completes. The RA0/INT, TMR0, or T0CKI

interrupt ag is automatically cleared or

the

pending

peripheral

interrupt

is

acknowledged.

7.2.2

TABLE WRITE CODE

The “i” operand of the TABLWT instruction can specify

that the value in the 16-bit TBLPTR register is auto-

matically

incremented

for

the

next

write.

In

Example 7-1, the TBLPTR register is not automatically

incremented.

EXAMPLE 7-1:

TABLE WRITE

CLRWDT

; Clear WDT

MOVLW

HIGH (TBL_ADDR) ; Load the Table

MOVWF

TBLPTRH

;

address

MOVLW

LOW (TBL_ADDR)

;

MOVWF

TBLPTRL

;

MOVLW

HIGH (DATA)

; Load HI byte

TLWT

1, WREG

;

in TABLATCH

MOVLW

LOW (DATA)

; Load LO byte

TABLWT

0,0,WREG

;

in TABLATCH

;

and write to

;

program memory

;

(Ext. SRAM)

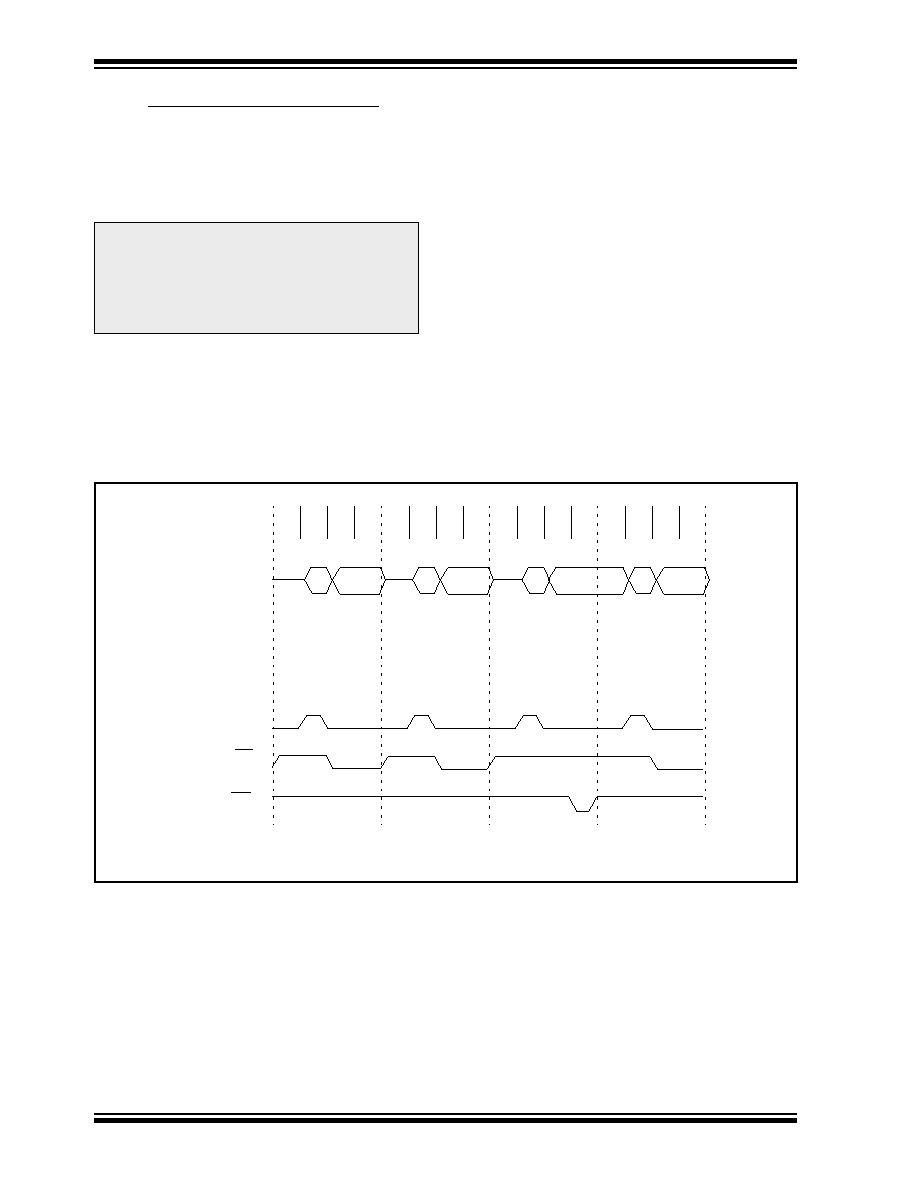

FIGURE 7-5:

TABLWT WRITE TIMING (EXTERNAL MEMORY)

Q1 Q2 Q3 Q4

AD15:AD0

Instruction

fetched

Instruction

executed

ALE

OE

WR

TABLWT

INST (PC+1)

INST (PC-1)

TABLWT cycle1

TABLWT cycle2

INST (PC+2)

Data write cycle

'1'

PC

PC+1

TBL

PC+2

Data out

INST (PC+1)

Note:

If external write GLINTD = '1', Enable bit = '1', '1'

→ Flag bit, Do table write. The highest pending interrupt is cleared.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24HJ256GP210-I/PT

IC PIC MCU FLASH 128KX16 100TQFP

PIC24HJ128GP310A-I/PF

IC PIC MCU FLASH 128KB 100-TQFP

DSPIC33FJ128GP310-I/PF

IC DSPIC MCU/DSP 128K 100TQFP

PIC16C66-20I/SO

IC MCU OTP 8KX14 PWM 28SOIC

DSPIC33FJ128MC510-I/PT

IC DSPIC MCU/DSP 128K 100TQFP

PIC16C66-20I/SP

IC MCU OTP 8KX14 PWM 28DIP

PIC18LF2620-I/SP

IC MCU FLASH 32KX16 28SDIP

PIC16F877-04I/P

IC MCU FLASH 8KX14 EE 40DIP

相关代理商/技术参数

PIC18F4620-I/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 DIP40

PIC18F4620-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 TQFP44

PIC18F4620T-I/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620T-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4680-E/ML

功能描述:8位微控制器 -MCU 64KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4680-E/P

功能描述:8位微控制器 -MCU 64KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT